Intel雖然還沒有在移動領域佔領大片疆土,但已經對ARM構成了嚴重的威脅,其雄厚的實力更是不容小覷,迫使ARM不得不加快的腳步,比如說高性能CPU架構就迅速從A57升級到了A72。

ARM架構的最大特點就是超低功耗、超小面積,A72又能小到什麼程度呢?

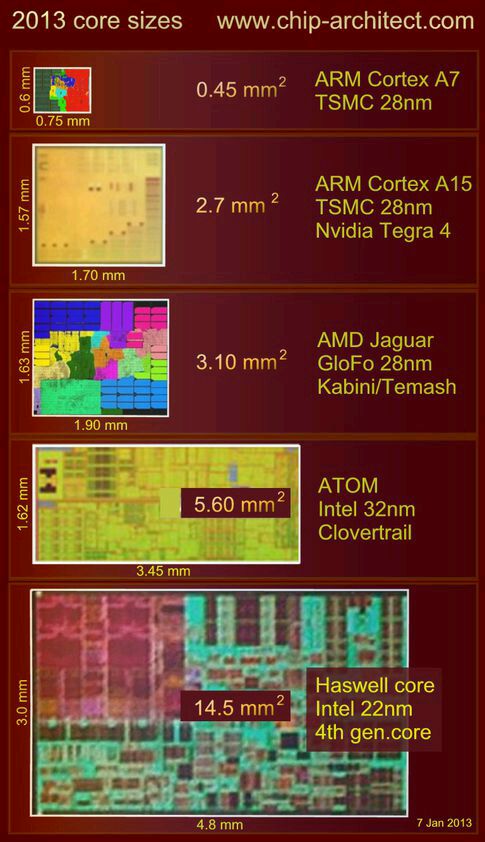

按照ARM的官方說法,A72如果使用台積電16nm FinFET工藝製造,單個核心面積僅為1.15平方毫米左右,相比之下Intel 14nm工藝製造的Broadwell,單個核心加上256KB二級緩存的面積達到了8平方毫米。

當然,如果要帶上二級緩存,那麼都得帶上才公平。四個A72核心加上2MB二級緩存的面積才是8平方毫米,與單個Broadwell單個核心加緩存相當。

性能自然是另外一回事兒了,不在本文討論範圍之內。

另外,Broadwell早已經商用,Skylake家族都馬上要來了,A72明年能成真就不錯了。

只看到Die SIZE晶片面積小能夠省錢根本看不到晶圓製造的本質

個人心得晶圓製造的本質是什麼?為什麼摩爾定律需要不斷演進製程,例如32nm -> 22nm ->14nm,

主要有三個目的

1.第一個原因是提高效能,把晶片面積做大了和電晶體使用數量提高固然性能可以上去,副作用是同樣尺寸的晶圓切割出的IC數量更少,也就是製造成本增加的原因 例如是12吋晶圓 一塊晶片如果100mm^2大小你可以用圓面積公式R^2*PI算出大約能切割多少數量的IC,所以半導體製程演進主要是在同樣大小的面積下提高效能而不是盲目的搞大核心降低量率和增加成本來提高效能。

2.第二個原因是降低功耗,電晶體用的越多假設時脈不變那樣,功耗也會越大

3.第三是降低成本 如果能用很小的IC就達成別人巨大的IC就達成的功能和效能 還更省電

這樣的競爭優勢就表示這個IC的架構/微架構很有效率

在同樣製程底下以上三個條件只能同時達到兩個,這就是摩爾定律的本質

只有3種設計晶片的思路,也是看出一個架構優不優秀的標準

1.降低成本 降低功耗 但是犧牲效能 例子:ARM A7 ARM A53

2.提高效能 降低功耗 但是犧牲成本增加IC的DIE大小

例子是頻果的A8 架構Cyclone gen 2 以同頻效能更高和電晶體的增加來換取效能

3.提高效能 降低成本 但是犧牲功耗 把晶片的時脈拉高到2.5GHz

正常來說架構設計不管多優秀,魚和熊掌不能兼得3者只能選其二,這也是製程要微縮的原因

這也是X86在移動市場失敗的主因,因為他太浪費電晶體了,要不是英特爾的製程和晶圓廠製程比較小,X86在同樣的製程底下根本是輸給ARM的,因為面積更大 耗電更高 同頻效能還不一定能贏的過

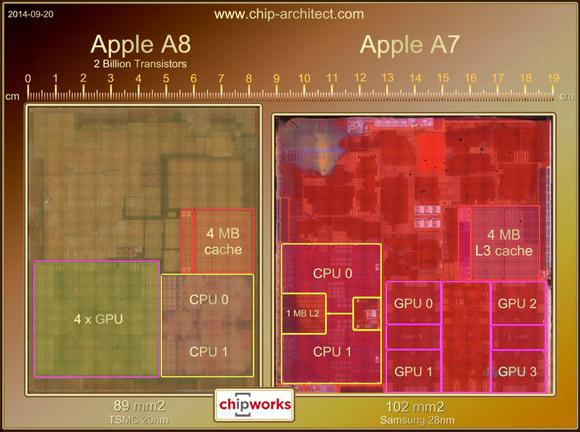

之前頻果的A8處理器被人批評說DIE很大 電晶體20億 ,電晶體數量很接近英特爾的Core

但是實際上即使是A8他的CPU核心+快取也不到整顆晶片面積的17%

因為A8是一顆SOC而包含了基頻 DSP GPU等等處理器 把這些扣掉

ARM面積還是遠低於X86的,而Intel haswell或是14nm BraswellCPU大約佔了1/3面積

、快取佔了1/3 、另外1/3是GPU,所以實際上X86在用了最新的製程下仍然比ARM面積大 功耗越更高 效能也沒贏過A8X,這種架構的先天缺陷是來自於以下幾個原因,

X86的歷史包袱

1.指令向前兼容性因為X86要兼容那些1980年代早就不使用的指令佔了80%的解碼單元的面積的指令其實只有不到20%的時間會利用到,而有80%的時間會用到20%的指令,這根本是一種浪費

2.指令轉碼成微指令在內部實作RISC又多一道程序

3.X86指令長度不對稱造成的分支預測命中率低

我預言ARM架構的效能在2018年會超過同時代的X86 Core I7等級桌上型電腦

A8X辦不到 但是A9X會很接近I5 A10X就差不多了