EUV 光源有四種

LPP Laser-produced Plasma 高亮度低碎屑LPP EUV 光源基於快速旋轉的液態金屬靶 , ASML EUV 250W

SR 同步輻射 功率很小

SRF-FEL

SSMB => 中國清大和德國 就 很多片 討論SSMB EUV ..

看 YOUTUBE 發現 , GAA 下已經 出現新的 MOS. C-FET .

28nm 是 bulk CMOS , 就傳統 CMOS , 用 DUV 機 193nm 光波可曝到 40nm ,

SMIC 用多重曝光 40nm => 20nm 再多一次曝光 => 10nm 再來一次曝光 => 極限 5nm .

TSMC 說 考慮到生產 應該7nm 就差不多 , 曝太多解析度會下降 良率不好 .再來是 EUV 13.5nm 波長 可曝 3nm . 至於為何193nm 跳到 13.5nm ? GOOGLE 找到說 157nm 的光,很容易被各吸收掉曝光性能很不好要抽成真空 業界放棄了157nm ,最後找到 13.5nm , 但 EUV 光還是被吸收得很高..電轉光 效率很低 很吃電的 .

28nm 得改 Finfet , 美國胡博士發明 , google FINFET 看到了 ,

美國加州大學柏克萊分校胡正明、金劉(Tsu-Jae King-Liu)、波科(Jerey Bokor)等三位教授發明了「鰭式場效電晶體」 , 而 胡正明教授 學生就 梁夢松..如果當年 UMC 找梁去開發 , 或許 UMC 可慢慢追趕 TSMC .

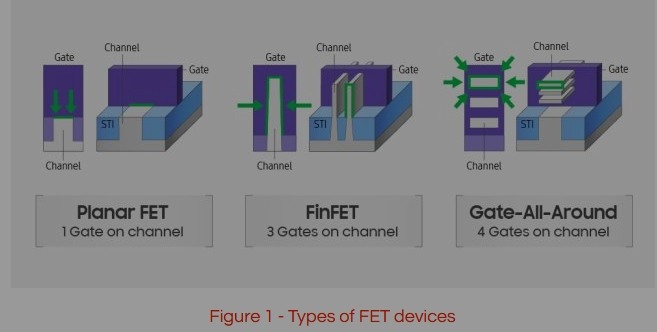

finfet (Intel 叫 Tri-Gate) => nanosheet (或叫 GAA) Intel 叫 Nanowire/Nanoribbon Transistors => forksheet

=> CFET

gate-all-around (GAA) nanoribbon FET 環繞式閘極場效電晶體(GAA-FET),該技術透過降低供電電壓級以及增加驅動電流能力以提升性能

GAAFET有多種不同的稱謂,例如有人稱nanosheet FET,Intel則稱其為RibbonFET。GAA結構電晶體的本質,就是把FinFET的fin轉90°,然後把多個fin橫向疊起來

planar FET 舊傳統的bulk CMOS , 縮到 20nm 需 立起來的 鰭式場效電晶體 FINFET , 但 3nm 再往下時 , 光這樣還不夠 . 須把 gate 包圍起來 就叫 GAA . 不同家有不同說法和做法 . nanosheet , nanowire 都類似 只是做法不太同 .

https://www.copperpodip.com/post/gate-all-around-gaa-fet-going-beyond-the-3-nanometer-mark

本來以為 GAA 應該人類極限了 , 前些日子看 清大教授 YOUTUBE 影片 , 才發現 竟然還有 堆疊起來 CFET ,

分 SEQUENCE CFET 跟monolithic CFET

Design-technology co-optimization of sequential and monolithic CFET as enabler of technology node beyond 2nm

complementary FET 極限了嗎??

)

)