loki6865 wrote:

3D堆疊技術Intel也是早有,

怎反是AMD先行用上了?

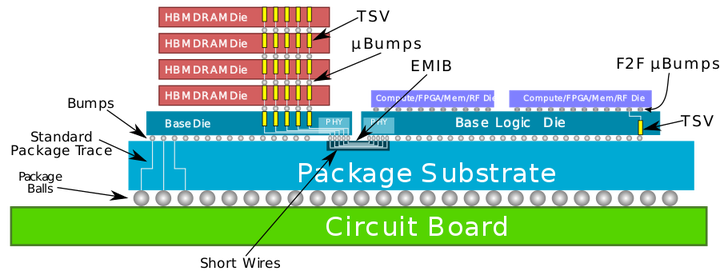

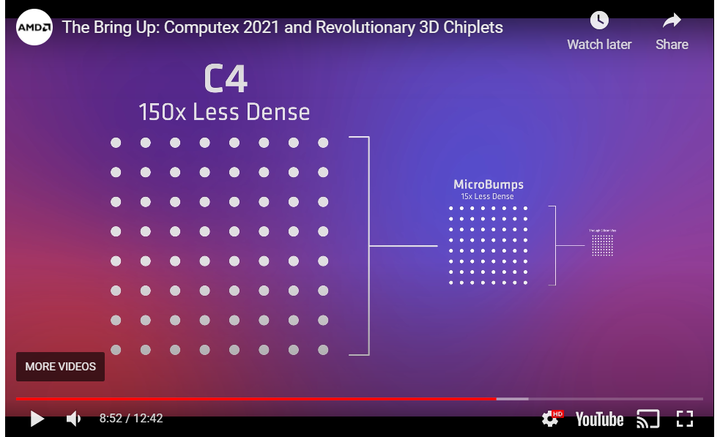

Intel的Foveros 3D堆叠用的是36微米的microbump,台積電是直接透過矽穿孔的TSV,連接密度比它高15倍。

游戏脑力 wrote:

近日,有推特用户@Kepler_L2发现,AMD在2019年12月提交了新的专利申请

游戏脑力 wrote:

到了zen5 amd的纯大核面对intel的大小核肯定玩不下去 势必要改变策略迎合intel的大方向

。那要不就考慮一下AMD不是在抄,又不可能。

。那要不就考慮一下AMD不是在抄,又不可能。 這個故事要這樣講才像話:

這個故事要這樣講才像話: