不過注意,MLID的曝料往往都很勁爆,但是精準度不敢完全保證。

按照他的說法,Zen6的桌面版代號為“Olympic Ridge”,不是之前傳聞的“Meduasa Ridge”,主流移動版的代號則確實是“Medusa Point”。

AMD Zen6仍將是CCD+IOD的組合式設計,其中CCD升級為3nm級工藝,大機率台積電N3E(Intel用的是N3B)——之前傳聞過2nm,但應該是EPYC版本的。

IOD部分升級為4nm級工藝,但不是來自台積電,而是交給三星代工,極可能是4LPP版本,用上了EUV極紫外光刻。

銳龍的CCD一直是都是單個8核心設計,這一次終於升級12核心,三級快取將順應地從32MB增加到48MB,因此我們將會在主流桌面上看到24核心型號。

如果再疊加64MB 3D快取,二級快取維持每核心1MB,那麼我們將看到恐怖的184MB快取,也就是24MB+96MB+64MB!

同時,以往的CCD都通過Infinity Fabirc匯流排連接IOD,而兩個CCD之間沒有直接互連,因此如果跨CCD的延遲一直比較高。

Zen6時代,兩個CCD將通過一種新的低延遲橋接匯流排彼此打通,徹底解決這一頑疾。

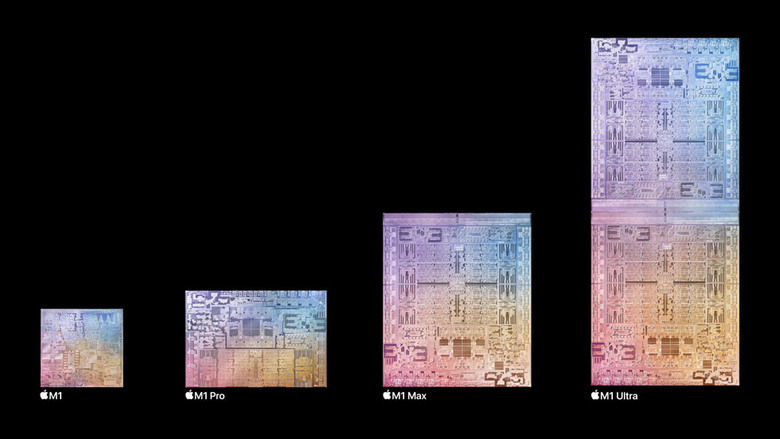

正因如此,未來的兩個CCD之間、CCD與IOD之間將不再相隔一段距離,而是緊緊挨在一起。

IOD部分除了升級工藝,也會升級GPU、記憶體甚至是PCIe。

記憶體現在可以支援DDR5-8000甚至更高,但需要1:2分頻,否則的話甜點頻率在DDR5-6200/6400左右,而下代分頻的話可以達到甚至超過DDR5-10000,不分頻也會更高但暫無具體數字。

GPU方面,有望升級到RDNA4架構,計算單元最多還是16個,搭配大容量二級快取。

PCIe方面不確認,可能升級PCIe 5.0,也可能增加更多通道。

移動版的Medusa Point也將是chiplets,共享同樣的CCD、IOD,不過是單個CCD配單個IOD,也就是最多12個核心。

CCD、IOD二者同樣肩並肩,但是AMD並沒有可以增加填充模組,將它補為方形。

最後,NPU AI引擎當然也會在現有全球最強的基礎上,繼續加強,但具體情況不詳,猜測桌面端有望達到目前的50 TOPS。